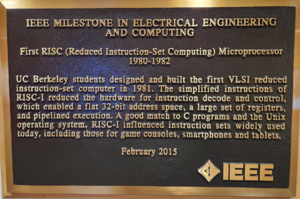

Milestones:First RISC (Reduced Instruction-Set Computing) Microprocessor 1980-1982

- Date Dedicated

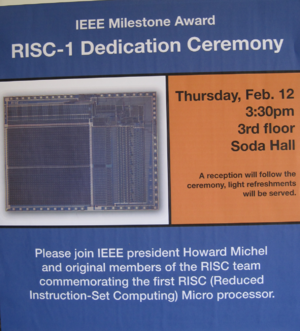

- 2015/02/12

- Dedication #

- 152

- Location

- Berkeley, California, U.S.A.

- IEEE Regions

- 6

- IEEE sections

- Oakland-East Bay

- Achievement date range

- 1980-1982

Title

First RISC (Reduced Instruction-Set Computing) Microprocessor 1980-1982

Citation

UC Berkeley students designed and built the first VLSI reduced instruction-set computer in 1981. The simplified instructions of RISC-I reduced the hardware for instruction decode and control, which enabled a flat 32-bit address space, a large set of registers, and pipelined execution. A good match to C programs and the Unix operating system, RISC-I influenced instruction sets widely used today, including those for game consoles, smartphones and tablets.

Street address(es) and GPS coordinates of the Milestone Plaque Sites

- Site 1: 387 Soda Hall: on the University of California-Berkeley campus at the NW corner of Hearst Ave. and LeRoy Ave., Berkeley CA 94720 US (GPS: 37.875624, -122.258882)

- Site 2: Computer History Museum, 1401 N. Shoreline Blvd, Mountain View, CA 94043 US, (37.414757, -122.077679)

Details of the physical location of the plaque

- Site 1: In the 3rd floor central corridor of Soda Hall, on the wall opposite the entrance to the Hewlett-Packard Auditorium, to the left of the later-dedicated IEEE Standard 754 Milestone plaque.

- Site 2: On the inside face of the front patio brick wall, near the museum's Main Entrance.

How the plaque site is protected/secured

- Site 1: Soda Hall is a UC Berkeley building of lecture halls and classrooms which houses the Computer Science Division and EECS Department offices. Building security is provided by the University of California Police.

- Site 2: Building security; 24/7 access.

Historical significance of the work

In the 1970s, the general trend in in computer design was to increase the complexity of computer architectures. The thought was that this would best exploit the rapidly advancing capabilities of semiconductor technology. The popular DEC VAX 11-780 was the leading example. About 280 machine-language instructions were implemented in the VAX hardware. The VAX 11-780, a so-called super minicomputer, was advertised as exercising 1 million instructions/second and sold for about $100,000. This class of computers was then termed CISCs, or complex instruction set computers.

Professors David Patterson and Carlo Sequin of the University of California at Berkeley observed that compilers for high-level computer languages, such as C, rarely utilized the added instructions. They thought that overall performance could be improved by optimizing the combination of processor function and memory on a single chip. Better overall performance at a much lower cost might be achieved by simplifying the processor, thereby allowing more chip area to be devoted to memory. Thus the goal was defined as a RISC, or reduced instruction set computer.

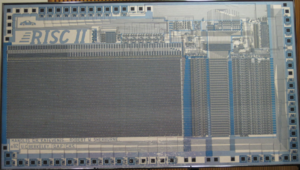

The RISC-I project was initiated in 1980 with assignments in a sequence of graduate classes at Berkeley, aiming to validate the RISC hypothesis. Initial conclusions based on simulation were positive, so the project continued, with critical grant support from DARPA. Students designed a processor with just 31 instructions, each executed in a single clock cycle. Included on the same student-designed chip, were 78 32-bit registers. This was enough memory to enable one-cycle execution of a large fraction of the instructions in compiled code.

Early in the project, the Berkeley team learned of previously unpublished work at IBM around 1975, led by Dr. John Cocke. The IBM 801, never commercialized, pioneered architectural principles similar to those independently chosen by the Berkeley team, though the goals for the 801 were quite different. Dr. Cocke visited Berkeley in 1981 and spoke to the student-faculty team. He gave them enthusiastic encouragement for their undertaking.

The first student-designed RISC-I chips, realized via the DARPA and NSF-funded MOSIS implementation service, were received in the fall of 1981. They were functional, though with minor deficiencies. However, performance was sufficient to convince previous skeptics to recognize the merits of the RISC approach to design of very large scale integrated (VLSI) computing. After correction of minor design bugs, the RISC-I design proved to outperform the VAX on almost every real-world benchmark.

No patents for the RISC-I design were sought for the Berkeley project. The earlier design of the IBM 801 might have been an impediment, though it had not been publicly disclosed. But the Berkeley team, funded primarily by government agencies, admirably chose to place their results in the public domain. This decision proved to be important to the later widespread adoption of the basic RISC concepts.

The RISC design was first commercialized as the SPARC microprocessor, introduced in 1987. Professor Patterson served as a consultant to Sun Microsystems, assisting Sun in development of the powerful RISC-based SPARC workstations. The SPARC workstations became a leading tool in the design of integrated circuits. Sun is now a part of the Oracle Corporation.

A similar project was carried on at about the same time at Stanford University, led by Professor John Hennessey. Professors Hennessey and Patterson are long-term friends and collaborators. They are co-authors of the leading textbook on computer architecture. The Stanford project produced a similar RISC processor design, termed MIPS. Also, there were important improvements to the compiler. The MIPS design was successfully commercialized by MIPS Computer Systems, founded by Professor Hennessey and others. That company subsequently was acquired by Silicon Graphics, Inc. The MIPS architecture is widely produced for a range of applications, under license from the company.

Along another path, Advanced RISC Machines (ARM) in the UK developed a continuing series of VLSI RISC processor designs that now are produced under license by leading semiconductor manufacturers of chips for use in game consoles, smart phones, and tablet computers. You may well be carrying one of these products today.

Not to be overlooked, the academic projects at Berkeley and Stanford educated scores of creative and talented Master’s degree and Doctoral students who became the next generation of technology leaders.

Obstacles (technical, political, geographic) that needed to be overcome

The largest obstacle in 1980 was skepticism among knowledgeable professionals, friendly or otherwise. No one on the team had prior experience designing VLSI computer processor chips. Professors Patterson and Sequin had the courage to continue. Of course, the work would not have been possible without the major support of DARPA and MOSIS.

Features that set this work apart from similar achievements

The IBM work begun in 1975, led by Dr. John Cocke, was aimed the control requirements for an electronic telephone central switch. That project influenced by Dr. Cocke’s recognition that compilers of that era rarely made use of complex high-level language instructions. A working model was built with off-the-shelf emitter-coupled logic (ECL) chips. There was no recognition of the benefit of combining many fast registers on the same chip as the central processor, and no attention to the possibility of an inexpensive single-chip microprocessor.

The MIPS project, led by Prof. John Hennessey at Stanford, featured important attention to the role of the compiler in making best use of RISC processor resources. The first working chip resulting from that project came about a year after RISC-I at Berkeley.

Significant references

Patterson, David A., and David R. Ditzel, "The case for the reduced instruction set computer." ACM SIGARCH Computer Architecture News 8.6 (1980): 25-33.

Patterson, David A., and Carlo H. Sequin, "RISC I: A reduced instruction set VLSI computer." Proceedings of the 8th annual symposium on Computer Architecture, IEEE Computer Society Press, 1981. Patterson, David A., and Carlo H. Sequin, “Design and Implementation of RISC I” UC Berkeley EECS Technical Report CSD-82-106, 1982. (Also appeared in Proc. Advanced Course on VLSI Architecture, University of Bristol, England, July 19-30, 1982.)

Patterson, David A., and Carlo H. Sequin, "A VLSI RISC." IEEE computer 15.9 (1982): 8-21. Digital Object Identifier: 10.1109/MC.1982.1654133

Sherburne, R. W., Katevenis, M. G., Patterson, D. A., & Sequin, C. H. (1984), “A 32-bit NMOS microprocessor with a large register file,” Solid-State Circuits, IEEE Journal of,19(5), 682-689. Digital Object Identifier: 10.1109/JSSC.1984.1052208

Patterson, David A. "Reduced instruction set computers." Communications of the ACM 28.1 (1985): 8-21.

Supporting materials

Map